WikiDer > Расширение размера страницы

Эта статья нужны дополнительные цитаты для проверка. (Октябрь 2012 г.) (Узнайте, как и когда удалить этот шаблон сообщения) |

В вычисление, Расширение размера страницы (PSE) относится к функции x86 процессоры, которые позволяют страницы больше традиционных 4 KiB размер. Он был введен в оригинале Pentium процессор, но это было публично задокументировано только Intel с выпуском Pentium Pro.[1] В CPUID инструкцию можно использовать для определения наличия PSE на x86 Процессоры.[2]

Мотивация

Представьте себе следующий сценарий. Прикладная программа запрашивает 1МиБ блок памяти. Чтобы выполнить этот запрос, операционная система, поддерживающая разбиение на страницы и работающая на более старых x86 CPU придется выделить 256 страницы по 4 КБ каждая. Для обслуживания каталогов страниц и таблиц страниц требуются накладные расходы в размере 1 КиБ памяти.

При доступе к этой памяти размером 1 МБ каждая из 256 записей страниц будет кэшироваться в резервный буфер перевода (TLB; кэш, который запоминает преобразования виртуального адреса в физические адреса для более быстрого поиска при последующих запросах памяти). Загромождение TLB, возможно, является одним из самых больших недостатков наличия нескольких записей страниц для того, что можно было бы разместить в одном блоке памяти. Если TLB будет заполнен, то запись TLB должна быть освобождена, каталог страниц и таблицы страниц должны быть «пройдены» в памяти, и, наконец, будет осуществлен доступ к памяти, и новая запись будет внесена в TLB. . Это серьезное снижение производительности и, возможно, было самым большим стимулом для расширения архитектуры x86 за счет увеличения размеров страниц.

PSE позволяет существовать страницам размером 4 МиБ вместе со страницами 4 КиБ. Описанный ранее запрос в 1 МиБ можно легко выполнить с помощью одной страницы размером 4 МиБ, и для этого потребуется только одна запись TLB. Однако недостатком использования больших размеров страниц является внутренняя фрагментация.

Операция

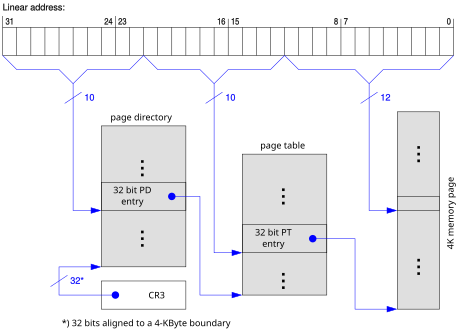

В традиционном 32-битном защищенный режим, процессоры x86 используют двухуровневую схему перевода страниц, где контрольный регистр CR3 указывает на один 4 КиБ длиной каталог страниц, который разделен на записи размером 1024 × 4 байта, которые указывают на длину 4 КиБ таблицы страниц, аналогичным образом состоящий из записей размером 1024 × 4 байта, указывающих на страницы длиной 4 КиБ.

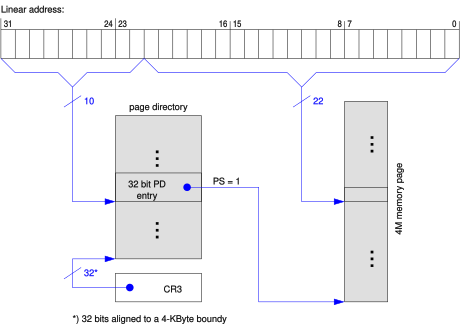

Включение PSE (установив бит 4, PSE, системного реестра CR4) меняет эту схему. Записи в каталоге страниц имеют дополнительный флаг в бите 7 с именем PS (за размер страницы). Этот флаг игнорировался без PSE, но теперь запись каталога страниц с PS, установленным в 1, указывает не на таблицу страниц, а на одну большую страницу размером 4 МиБ. Запись каталога страниц с PS, установленным в 0, ведет себя как без PSE.

Если новее PSE-36 возможность доступна на ЦП, что проверено с помощью CPUID инструкции, тогда еще 4 бита в дополнение к обычным 10 битам используются внутри записи каталога страниц, указывающей на большую страницу. Это позволяет разместить большую страницу в 36-битном адресном пространстве.

Если Расширение физического адреса (PAE), размер больших страниц уменьшается с 4 до 2 МБ, а PSE всегда включен, независимо от бита PSE в CR4.

Рекомендации

- ^ Т. Шенли (1998). Системная архитектура Pentium Pro и Pentium II. Эддисон-Уэсли Профессионал. п.439. ISBN 978-0-201-30973-7.

- ^ Руководство разработчика программного обеспечения для архитектур Intel 64 и IA-32, том 3A. Intel Корпорация. Август 2007. С. 3–26–3–28.