WikiDer > UltraSPARC - Википедия

Эта статья включает Список ссылок, связанное чтение или внешняя ссылка, но его источники остаются неясными, потому что в нем отсутствует встроенные цитаты. (Ноябрь 2017 г.) (Узнайте, как и когда удалить этот шаблон сообщения) |

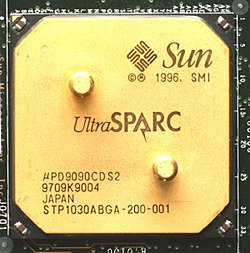

Микропроцессор UltraSPARC 200 МГц | |

| Общая информация | |

|---|---|

| Запущен | 1995 |

| Снято с производства | 1997 |

| Разработано | Sun Microsystems |

| Спектакль | |

| Максимум. ЦПУ тактовая частота | От 143 МГц до 200 МГц |

| Архитектура и классификация | |

| Набор инструкций | SPARC V9 |

| Физические характеристики | |

| Ядра |

|

| История | |

| Предшественник | SuperSPARC II |

| Преемник | UltraSPARC II |

В UltraSPARC это микропроцессор разработан Sun Microsystems и изготовлен Инструменты Техаса, представленный в середине 1995 года. Это первый микропроцессор Sun, в котором реализована 64-разрядная SPARC V9 архитектура набора команд (ЭТО). Марк Трембле был со-микроархитектором.

Микроархитектура

UltraSPARC состоит из четырех выпусков суперскалярный микропроцессор, который выполняет инструкции в чтобы. Он имеет девятиступенчатое целое число трубопровод.

Функциональные блоки

Исполнительные блоки были упрощены по сравнению с SuperSPARC для достижения более высоких тактовых частот - примером упрощения является то, что ALU не были каскадированы, в отличие от SuperSPARC, чтобы избежать ограничения тактовой частоты.

Целое число зарегистрировать файл имеет 32 64-битных записи. Поскольку SPARC ISA использует зарегистрировать окна, из которых у UltraSPARC восемь, фактическое количество регистров составляет 144. Файл регистров имеет семь портов чтения и три порта записи. Целочисленный регистровый файл предоставляет регистры для двух арифметико-логические устройства и блок загрузки / хранения. Оба ALU могут выполнять арифметические, логические инструкции и инструкции сдвига, но только один может выполнять инструкции умножения и деления.

Блок с плавающей запятой состоит из пяти функциональных блоков. Один выполняет сложение и вычитание с плавающей запятой, один умножает, третий делит и извлекает квадратный корень. Два модуля предназначены для выполнения инструкций SIMD, определенных Набор визуальных инструкций (ВИС). Файл регистров с плавающей запятой содержит тридцать два 64-битных регистра. Он имеет пять портов чтения и три порта записи.

Кеш

UltraSPARC имеет два уровня кэша: первичный и вторичный. Есть два основных кэша, один для инструкций и один для данных. Оба имеют емкость 16 КБ.

UltraSPARC требовал обязательного внешнего вторичного кеша. Кэш унифицирован, имеет объем от 512 КБ до 4 МБ и имеет прямое отображение. Он может возвращать данные за один цикл. Внешний кэш реализован с помощью синхронных SRAM, работающих на той же частоте, что и микропроцессор, поскольку соотношения не поддерживаются. Доступ к нему осуществляется через шину данных.

Изготовление

Он содержал 3,8 миллиона транзисторов. Он был изготовлен по технологии EPIC-3 компании Texas Instruments, толщина 0,5 мкм. комплементарный металл – оксид – полупроводник (CMOS) процесс с четырьмя уровнями металла. UltraSPARC не производился в BiCMOS Процесс, поскольку Texas Instruments заявила, что он плохо масштабируется до процессов 0,5 мкм и дает небольшое улучшение производительности. Процесс был отточен на MVP компании TI. цифровой сигнальный процессор (DSP) с отсутствием некоторых функций, таких как три уровня металла вместо четырех и размер элемента 0,55, прежде чем он был использован для изготовления UltraSPARC, чтобы избежать повторения проблем изготовления, с которыми столкнулись SuperSPARC.

Упаковка

UltraSPARC упакован в пластик с контактом 521 контакт. массив сетки мячей (PBGA).

Связанные процессоры

Рекомендации

- Гринли, Д. и др. (1995). «UltraSPARC: суперскалярный 64-разрядный SPARC следующего поколения». Материалы Compcon '95: С. 442–451.

- Гвеннап, Линли (3 октября 1994 г.). «UltraSparc раскрывает возможности SPARC». Отчет микропроцессора, Том 8, номер 13.

- Гвеннап, Линли (5 декабря 1994 г.). «UltraSparc добавляет мультимедийные инструкции». Отчет микропроцессора.