WikiDer > Обнаружение последовательного присутствия

В вычисление, обнаружение серийного присутствия (СПД) - это стандартизированный способ автоматического доступа к информации о модуль памяти. Ранее 72-контактный SIMM включены пять контактов, которые обеспечивают пять бит параллельное обнаружение присутствия (PPD) данные, но 168-контактный DIMM стандарт изменен на последовательное обнаружение присутствия, чтобы закодировать гораздо больше информации.[1]

Когда обычный современный компьютер включается, он начинает с самотестирование при включении (ПОЧТОВЫЙ). Примерно с середины 1990-х годов этот процесс включает в себя автоматическую настройку оборудования, имеющегося в настоящее время. SPD - это аппаратная функция памяти, которая позволяет компьютеру узнать, какая память присутствует, а какая тайминги памяти использовать для доступа к памяти.

Некоторые компьютеры полностью автоматически адаптируются к изменениям оборудования. В большинстве случаев существует специальная необязательная процедура для доступа BIOS параметры, чтобы просмотреть и, возможно, внести изменения в настройки. Возможно, удастся управлять тем, как компьютер использует данные SPD в памяти - для выбора настроек, выборочного изменения таймингов памяти или, возможно, для полной отмены данных SPD (см. разгон).

Сохраненная информация

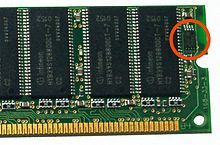

Для модуля памяти, поддерживающего SPD, JEDEC стандарты требуют, чтобы определенные параметры были в младших 128 байтах EEPROM расположен на модуле памяти. Эти байты содержат параметры синхронизации, производителя, серийный номер и другую полезную информацию о модуле. Устройства, использующие память, автоматически определяют ключевые параметры модуля, считывая эту информацию. Например, данные SPD на SDRAM модуль может предоставить информацию о Задержка CAS так что система может установить это правильно без вмешательства пользователя.

Доступ к SPD EEPROM осуществляется с помощью SMBus, вариант I²C протокол. Это сокращает количество коммуникационных контактов на модуле до двух: тактовый сигнал и сигнал данных. EEPROM использует общие контакты заземления с RAM, имеет собственный вывод питания и три дополнительных контакта (SA0–2) для идентификации слота, которые используются для присвоения EEPROM уникального адреса в диапазоне 0x50–0x57. Линии связи могут использоваться не только 8 модулями памяти, одна и та же шина SMBus обычно используется на материнских платах для задач мониторинга состояния системы, таких как считывание напряжения источника питания, ЦПУ температуры и скорости вращения вентилятора.

EEPROM SPD также отвечают на адреса I²C 0x30–0x37, если они не были защищены от записи, а расширение (серия TSE) использует адреса 0x18–0x1F для доступа к дополнительному встроенному датчику температуры. Все эти ценности семибитные адреса I²C сформированный префиксом кода идентификатора типа устройства (DTIC) с SA0-2: для чтения (1100) из слота 3 используется 110 0011 = 0x33. С последним битом чтения / записи он формирует 8-битный код выбора устройства.[2] Обратите внимание, что семантика идентификатора слота отличается для операций защиты от записи: для них они могут вообще не передаваться контактами SA.[3]

До SPD микросхемы памяти обнаруживались с помощью параллельного обнаружения присутствия (PPD). PPD использовал отдельный вывод для каждого бита информации, что означало, что можно было сохранить только скорость и плотность модуля памяти из-за ограниченного пространства для выводов.

SDR SDRAM

Первая спецификация SPD была выпущена JEDEC и ужесточена Intel в рамках своей PC100 спецификация памяти.[4] Большинство значений указаны в двоично-десятичный форма. Самый значительный грызть может содержать значения от 10 до 15, а в некоторых случаях может быть выше. В таких случаях вместо этого используются кодировки для 1, 2 и 3 для кодирования 16, 17 и 18. Старший полубайт 0 зарезервирован для представления «неопределенного».

ПЗУ SPD определяет до трех таймингов DRAM для трех задержек CAS, заданных битами в байте 18. Сначала идет самая высокая задержка CAS (самая быстрая тактовая частота), затем две более низкие задержки CAS с постепенно снижающимися тактовыми частотами.

| Байт | Кусочек | Примечания | ||||||||

|---|---|---|---|---|---|---|---|---|---|---|

| (реш.) | (шестнадцатеричный) | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | |

| 0 | 0x00 | Количество присутствующих байтов | Обычно 128 | |||||||

| 1 | 0x01 | бревно2(размер SPD EEPROM) | Обычно 8 (256 байт) | |||||||

| 2 | 0x02 | Базовый тип памяти (4: SPD SDRAM) | ||||||||

| 3 | 0x03 | Банк 2 бит адреса строки (0-15) | Биты адреса строки банка 1 (1–15) | Банк 2 равен 0, если он совпадает с банком 1 | ||||||

| 4 | 0x04 | Биты адреса столбца банка 2 (0–15) | Биты адреса столбца банка 1 (1–15) | Банк 2 равен 0, если он совпадает с банком 1 | ||||||

| 5 | 0x05 | Количество банков RAM на модуле (1–255) | Обычно 1 или 2 | |||||||

| 6 | 0x06 | Младший байт ширины данных модуля | Обычно 64 или 72 для модулей DIMM с ECC | |||||||

| 7 | 0x07 | Ширина данных модуля, старший байт | 0, если ширина ≥ 256 бит | |||||||

| 8 | 0x08 | Уровень напряжения интерфейса этой сборки (не такой, как Vcc напряжение питания) (0–4) | Декодировано поиском в таблице | |||||||

| 9 | 0x09 | Наносекунды (0–15) | Десятые доли наносекунды (0,0–0,9) | Время цикла часов при максимальной задержке CAS | ||||||

| 10 | 0x0a | Наносекунды (0–15) | Десятые доли наносекунды (0,0–0,9) | Время доступа к SDRAM с часов (tAC) | ||||||

| 11 | 0x0b | Тип конфигурации DIMM (0–2): без ECC, четность, ECC | Поиск по таблице | |||||||

| 12 | 0x0c | Себя | Период обновления (0–5): 64, 256, 128, 32, 16, 8 кГц | Обновить требования | ||||||

| 13 | 0x0d | Банк 2 2 × | Ширина первичной SDRAM банка 1 (1–127, обычно 8) | Ширина устройств SDRAM данных банка 1. Банк 2 может иметь одинаковую ширину или 2 × ширину, если установлен бит 7. | ||||||

| 14 | 0x0e | Банк 2 2 × | Разрядность ECC SDRAM банка 1 (0–127) | Ширина устройств SDRAM с ECC / четностью банка 1. Банк 2 может иметь одинаковую ширину или 2 × ширину, если установлен бит 7. | ||||||

| 15 | 0x0f | Задержка часов для случайного чтения столбца | Обычно 1 | |||||||

| 16 | 0x10 | Страница | — | — | — | 8 | 4 | 2 | 1 | Поддерживаемые длины пакетов (растровое изображение) |

| 17 | 0x11 | Банков на устройство SDRAM (1–255) | Обычно 2 или 4 | |||||||

| 18 | 0x12 | — | 7 | 6 | 5 | 4 | 3 | 2 | 1 | CAS поддерживаются задержки (растровое изображение) |

| 19 | 0x13 | — | 6 | 5 | 4 | 3 | 2 | 1 | 0 | CS поддерживаются задержки (растровое изображение) |

| 20 | 0x14 | — | 6 | 5 | 4 | 3 | 2 | 1 | 0 | МЫ поддерживаются задержки (растровое изображение) |

| 21 | 0x15 | — | Избыточный | Diff. Часы | Зарегистрированные данные | Буферизованные данные | Встроенная ФАПЧ | Зарегистрированный адрес. | Буферизованный адрес. | Растровое изображение функции модуля памяти |

| 22 | 0x16 | — | — | Верхний Vcc (напряжение питания) допуск | Нижний Vcc (напряжение питания) допуск | Запись / 1 чтение | Предварительно зарядить все | Автоматическая предзарядка | Рано РАН предварительная зарядка | Функция чипа памяти поддерживает растровое изображение |

| 23 | 0x17 | Наносекунды (4–18) | Десятые доли наносекунды (0–9: 0,0–0,9) | Время такта при средней задержке CAS | ||||||

| 24 | 0x18 | Наносекунды (4–18) | Десятые доли наносекунды (0–9: 0,0–0,9) | Время доступа к данным с часов (tAC) | ||||||

| 25 | 0x19 | Наносекунды (1–63) | 0,25 нс (0–3: 0,00–0,75) | Время тактового цикла при короткой задержке CAS. | ||||||

| 26 | 0x1a | Наносекунды (1–63) | 0,25 нс (0–3: 0,00–0,75) | Время доступа к данным с часов (tAC) | ||||||

| 27 | 0x1b | Наносекунды (1–255) | Минимальное время предварительной зарядки ряда (тRP) | |||||||

| 28 | 0x1c | Наносекунды (1–255) | Минимальная задержка между активной строкой и активной строкой (tRRD) | |||||||

| 29 | 0x1d | Наносекунды (1–255) | Минимум РАН к CAS задержка (тУЗО) | |||||||

| 30 | 0x1e | Наносекунды (1–255) | Минимальное время от активного до предварительной зарядки (tРАН) | |||||||

| 31 | 0x1f | 512 МБ | 256 МБ | 128 МБ | 64 МБ | 32 МБ | 16 МБ | 8 МБ | 4 МБ | Плотность банка модулей (bitmap). Установлено два бита, если банки разного размера. |

| 32 | 0x20 | Знак (1: -) | Наносекунды (0–7) | Десятые доли наносекунды (0–9: 0,0–0,9) | Время установки адреса / команды с часов | |||||

| 33 | 0x21 | Знак (1: -) | Наносекунды (0–7) | Десятые доли наносекунды (0–9: 0,0–0,9) | Время удержания адреса / команды после часов | |||||

| 34 | 0x22 | Знак (1: -) | Наносекунды (0–7) | Десятые доли наносекунды (0–9: 0,0–0,9) | Установка времени ввода данных с часов | |||||

| 35 | 0x23 | Знак (1: -) | Наносекунды (0–7) | Десятые доли наносекунды (0–9: 0,0–0,9) | Время удержания ввода данных после часов | |||||

| 36–61 | 0x24–0x3d | Зарезервированный | Для будущей стандартизации | |||||||

| 62 | 0x3e | Основная версия (0–9) | Незначительная редакция (0–9) | Уровень ревизии СПД; например, 1.2 | ||||||

| 63 | 0x3f | Контрольная сумма | Сумма байтов 0–62, не затем отрицать | |||||||

| 64–71 | 0x40–47 | Производитель JEDEC id. | Хранится с прямым порядком байтов, завершение с нулевым дополнением | |||||||

| 72 | 0x48 | Место изготовления модуля | Код производителя | |||||||

| 73–90 | 0x49–0x5a | Номер детали модуля | ASCII, дополненный пробелами | |||||||

| 91–92 | 0x5b – 0x5c | Код версии модуля | Код производителя | |||||||

| 93 | 0x5d | Десятки лет (0–9: 0–90) | Годы (0–9) | Дата изготовления (YYWW) | ||||||

| 94 | 0x5e | Десятки недель (0–5: 0–50) | Недели (0–9) | |||||||

| 95–98 | 0x5f – 0x62 | Серийный номер модуля | Код производителя | |||||||

| 99–125 | 0x63–0x7f | Данные производителя | Может быть улучшен профиль производительности | |||||||

| 126 | 0x7e | 0x66 [sic] для 66 МГц, 0x64 для 100 МГц | Поддержка частоты Intel | |||||||

| 127 | 0x7f | CLK0 | CLK1 | CLK3 | CLK3 | 90/100 ° С | CL3 | CL2 | Параллельная точка доступа | Растровое изображение функции Intel |

DDR SDRAM

Формат DDR DIMM SPD является расширением формата SDR SDRAM. В основном диапазоны параметров масштабируются для соответствия более высоким скоростям.

| Байт | Кусочек | Примечания | ||||||||

|---|---|---|---|---|---|---|---|---|---|---|

| (реш.) | (шестнадцатеричный) | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | |

| 0 | 0x00 | Количество записанных байтов | Обычно 128 | |||||||

| 1 | 0x01 | бревно2(размер SPD EEPROM) | Обычно 8 (256 байт) | |||||||

| 2 | 0x02 | Базовый тип памяти (7 = DDR SDRAM) | ||||||||

| 3 | 0x03 | Банк 2 бит адреса строки (0-15) | Биты адреса строки банка 1 (1–15) | Банк 2 равен 0, если он совпадает с банком 1. | ||||||

| 4 | 0x04 | Биты адреса столбца банка 2 (0–15) | Биты адреса столбца банка 1 (1–15) | Банк 2 равен 0, если он совпадает с банком 1. | ||||||

| 5 | 0x05 | Количество банков RAM на модуле (1–255) | Обычно 1 или 2 | |||||||

| 6 | 0x06 | Младший байт ширины данных модуля | Обычно 64 или 72 для модулей DIMM с ECC | |||||||

| 7 | 0x07 | Ширина данных модуля, старший байт | 0, если ширина ≥ 256 бит | |||||||

| 8 | 0x08 | Уровень напряжения интерфейса этой сборки (не такой, как Vcc напряжение питания) (0–5) | Декодировано поиском в таблице | |||||||

| 9 | 0x09 | Наносекунды (0–15) | Десятые доли наносекунды (0,0–0,9) | Время цикла часов при максимальной задержке CAS. | ||||||

| 10 | 0x0a | Десятые доли наносекунды (0,0–0,9) | Сотые доли наносекунд (0,00–0,09) | Время доступа к SDRAM с часов (tAC) | ||||||

| 11 | 0x0b | Тип конфигурации DIMM (0–2): без ECC, четность, ECC | Поиск в таблице | |||||||

| 12 | 0x0c | Себя | Период обновления (0–5): 64, 256, 128, 32, 16, 8 кГц | Обновить требования | ||||||

| 13 | 0x0d | Банк 2 2 × | Ширина первичной SDRAM банка 1 (1–127) | Ширина устройств SDRAM данных банка 1. Банк 2 может иметь одинаковую ширину или 2 × ширину, если установлен бит 7. | ||||||

| 14 | 0x0e | Банк 2 2 × | Ширина ECC SDRAM банка 1 (0–127) | Ширина устройств SDRAM с ECC / четностью банка 1. Банк 2 может иметь одинаковую ширину или 2 × ширину, если установлен бит 7. | ||||||

| 15 | 0x0f | Задержка часов для случайного чтения столбца | Обычно 1 | |||||||

| 16 | 0x10 | Страница | — | — | — | 8 | 4 | 2 | 1 | Поддерживаемые длины пакетов (растровое изображение) |

| 17 | 0x11 | Банков на устройство SDRAM (1–255) | Обычно 4 | |||||||

| 18 | 0x12 | — | 4 | 3.5 | 3 | 2.5 | 2 | 1.5 | 1 | CAS поддерживаются задержки (растровое изображение) |

| 19 | 0x13 | — | 6 | 5 | 4 | 3 | 2 | 1 | 0 | CS поддерживаются задержки (растровое изображение) |

| 20 | 0x14 | — | 6 | 5 | 4 | 3 | 2 | 1 | 0 | МЫ поддерживаются задержки (растровое изображение) |

| 21 | 0x15 | — | Икс | Часы различий | Внешнее включение переключателя FET | Встроенный переключатель FET | Встроенная ФАПЧ | Зарегистрировано | Буферизованный | Растровое изображение функции модуля памяти |

| 22 | 0x16 | Быстрая точка доступа | Параллельная автоматическая предоплата | Верхний Vcc (напряжение питания) допуск | Нижний Vcc (напряжение питания) допуск | — | — | — | Включает слабый драйвер | Растровое изображение функции микросхемы памяти |

| 23 | 0x17 | Наносекунды (0–15) | Десятые доли наносекунды (0,0–0,9) | Время такта при средней задержке CAS. | ||||||

| 24 | 0x18 | Десятые доли наносекунды (0,0–0,9) | Сотые доли наносекунд (0,00–0,09) | Время доступа к данным с часов (tAC) | ||||||

| 25 | 0x19 | Наносекунды (0–15) | Десятые доли наносекунды (0,0–0,9) | Время тактового цикла при малой задержке CAS. | ||||||

| 26 | 0x1a | Десятые доли наносекунды (0,0–0,9) | Сотые доли наносекунд (0,00–0,09) | Время доступа к данным с часов (tAC) | ||||||

| 27 | 0x1b | Наносекунды (1–63) | 0,25 нс (0–0,75) | Минимальное время предварительной зарядки ряда (тRP) | ||||||

| 28 | 0x1c | Наносекунды (1–63) | 0,25 нс (0–0,75) | Минимальная задержка между активной строкой и активной строкой (tRRD) | ||||||

| 29 | 0x1d | Наносекунды (1–63) | 0,25 нс (0–0,75) | Минимум РАН к CAS задержка (тУЗО) | ||||||

| 30 | 0x1e | Наносекунды (1–255) | Минимальное время от активного до предварительной зарядки (tРАН) | |||||||

| 31 | 0x1f | 512 МБ | 256 МБ | 128 МБ | 64 МБ | 32 МБ | 16 МБ / 4 ГиБ | 8 МБ / 2 ГиБ | 4 МБ / 1 ГиБ | Плотность банка модулей (bitmap). Установлено два бита, если банки разного размера. |

| 32 | 0x20 | Десятые доли наносекунды (0,0–0,9) | Сотые доли наносекунд (0,00–0,09) | Время установки адреса / команды с часов | ||||||

| 33 | 0x21 | Десятые доли наносекунды (0,0–0,9) | Сотые доли наносекунд (0,00–0,09) | Время удержания адреса / команды после часов | ||||||

| 34 | 0x22 | Десятые доли наносекунды (0,0–0,9) | Сотые доли наносекунд (0,00–0,09) | Установка времени ввода данных с часов | ||||||

| 35 | 0x23 | Десятые доли наносекунды (0,0–0,9) | Сотые доли наносекунд (0,00–0,09) | Время удержания ввода данных после часов | ||||||

| 36–40 | 0x24–0x28 | Зарезервированный | Информация о суперсете | |||||||

| 41 | 0x29 | Наносекунды (1–255) | Минимальное время активности / активности / обновления (tRC) | |||||||

| 42 | 0x2a | Наносекунды (1–255) | Минимальное время обновления до активного / времени обновления (tRFC) | |||||||

| 43 | 0x2b | Наносекунды (1–63 или 255: без максимума) | 0,25 нс (0–0,75) | Максимальное время цикла часов (tСК Максимум.) | ||||||

| 44 | 0x2c | Сотые доли наносекунд (0,01–2,55) | Максимальный перекос, DQS на любой DQ. (тDQSQ Максимум.) | |||||||

| 45 | 0x2d | Десятые доли наносекунды (0,0–1,2) | Сотые доли наносекунд (0,00–0,09) | Коэффициент перекоса удержания считываемых данных (tQHS) | ||||||

| 46 | 0x2e | Зарезервированный | Для будущей стандартизации | |||||||

| 47 | 0x2f | — | Высота | Высота модуля DIMM, поиск по таблице | ||||||

| 48–61 | 0x30–0x3d | Зарезервированный | Для будущей стандартизации | |||||||

| 62 | 0x3e | Основная версия (0–9) | Незначительная редакция (0–9) | Уровень ревизии SPD, 0,0 или 1,0 | ||||||

| 63 | 0x3f | Контрольная сумма | Сумма байтов 0–62, не затем отрицать | |||||||

| 64–71 | 0x40–47 | Производитель JEDEC id. | Хранится с прямым порядком байтов, завершение с нулевым дополнением | |||||||

| 72 | 0x48 | Место изготовления модуля | Код производителя | |||||||

| 73–90 | 0x49–0x5a | Номер детали модуля | ASCII, дополненный пробелами | |||||||

| 91–92 | 0x5b – 0x5c | Код версии модуля | Код производителя | |||||||

| 93 | 0x5d | Десятки лет (0–90) | Годы (0–9) | Дата изготовления (YYWW) | ||||||

| 94 | 0x5e | Десятки недель (0–50) | Недели (0–9) | |||||||

| 95–98 | 0x5f – 0x62 | Серийный номер модуля | Код производителя | |||||||

| 99–127 | 0x63–0x7f | Данные производителя | Может быть улучшен профиль производительности | |||||||

DDR2 SDRAM

В стандарт DDR2 SPD внесен ряд изменений, но он примерно аналогичен приведенному выше. Одно примечательное исключение - запутанная и мало используемая поддержка модулей DIMM с двумя уровнями разного размера.

Для полей времени цикла (байты 9, 23, 25 и 49), которые закодированы в BCD, некоторые дополнительные кодировки определены для десятой цифры, чтобы точно представить некоторые общие моменты времени:

| Шестигранник | Двоичный | Значимость |

|---|---|---|

| А | 1010 | 0.25 (¼) |

| B | 1011 | 0.33 (⅓) |

| C | 1100 | 0.66 (⅔) |

| D | 1101 | 0.75 (¾) |

| E | 1110 | 0.875 (⅞, расширение nVidia XMP) |

| F | 1111 | Зарезервированный |

| Байт | Кусочек | Примечания | ||||||||

|---|---|---|---|---|---|---|---|---|---|---|

| Декабрь | Шестигранник | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | |

| 0 | 0x00 | Количество записанных байтов | Обычно 128 | |||||||

| 1 | 0x01 | бревно2(размер SPD EEPROM) | Обычно 8 (256 байт) | |||||||

| 2 | 0x02 | Базовый тип памяти (8 = DDR2 SDRAM) | ||||||||

| 3 | 0x03 | Зарезервированный | Биты адреса строки (1–15) | |||||||

| 4 | 0x04 | Зарезервированный | Биты адреса столбца (1–15) | |||||||

| 5 | 0x05 | Вертикальная высота | Куча? | ConC? | Ранги − 1 (1–8) | Обычно 0 или 1, что означает 1 или 2 | ||||

| 6 | 0x06 | Ширина данных модуля | Обычно 64 или 72 для модулей DIMM с ECC | |||||||

| 7 | 0x07 | Зарезервированный | ||||||||

| 8 | 0x08 | Уровень напряжения интерфейса этой сборки (не такой, как Vcc напряжение питания) (0–5) | Декодируется поиском по таблице. Обычно 5 = SSTL 1,8 В | |||||||

| 9 | 0x09 | Наносекунды (0–15) | Десятые доли наносекунды (0,0–0,9) | Время цикла часов при максимальной задержке CAS. | ||||||

| 10 | 0x0a | Десятые доли наносекунды (0,0–0,9) | Сотые доли наносекунд (0,00–0,09) | Время доступа к SDRAM с часов (tAC) | ||||||

| 11 | 0x0b | Тип конфигурации DIMM (0–2): без ECC, четность, ECC | Поиск по таблице | |||||||

| 12 | 0x0c | Себя | Период обновления (0–5): 64, 256, 128, 32, 16, 8 кГц | Обновить требования | ||||||

| 13 | 0x0d | Ширина первичной SDRAM (1–255) | Обычно 8 (модуль построен из 8 частей) или 16 | |||||||

| 14 | 0x0e | Ширина ECC SDRAM (0–255) | Ширина банковских устройств SDRAM с ECC / четностью. Обычно 0 или 8. | |||||||

| 15 | 0x0f | Зарезервированный | ||||||||

| 16 | 0x10 | — | — | — | — | 8 | 4 | — | — | Поддерживаемые длины пакетов (растровое изображение) |

| 17 | 0x11 | Банков на устройство SDRAM (1–255) | Обычно 4 или 8 | |||||||

| 18 | 0x12 | 7 | 6 | 5 | 4 | 3 | 2 | — | — | CAS поддерживаются задержки (растровое изображение) |

| 19 | 0x13 | Зарезервированный | ||||||||

| 20 | 0x14 | — | — | Мини-UDIMM | Мини-RDIMM | Micro-DIMM | SO-DIMM | UDIMM | RDIMM | Тип DIMM этой сборки (растровое изображение) |

| 21 | 0x15 | — | Модуль аналитический зонд | — | Внешнее включение переключателя FET | — | — | — | — | Растровое изображение функции модуля памяти |

| 22 | 0x16 | — | — | — | — | — | — | — | Включает слабый драйвер | Растровое изображение функции микросхемы памяти |

| 23 | 0x17 | Наносекунды (0–15) | Десятые доли наносекунды (0,0–0,9) | Время такта при средней задержке CAS. | ||||||

| 24 | 0x18 | Десятые доли наносекунды (0,0–0,9) | Сотые доли наносекунд (0,00–0,09) | Время доступа к данным с часов (tAC) | ||||||

| 25 | 0x19 | Наносекунды (0–15) | Десятые доли наносекунды (0,0–0,9) | Время тактового цикла при малой задержке CAS. | ||||||

| 26 | 0x1a | Десятые доли наносекунды (0,0–0,9) | Сотые доли наносекунд (0,00–0,09) | Время доступа к данным с часов (tAC) | ||||||

| 27 | 0x1b | Наносекунды (1–63) | 1/4 нс (0–0,75) | Минимальное время предварительной зарядки ряда (тRP) | ||||||

| 28 | 0x1c | Наносекунды (1–63) | 1/4 нс (0–0,75) | Минимальная задержка между активной строкой и активной строкой (tRRD) | ||||||

| 29 | 0x1d | Наносекунды (1–63) | 1/4 нс (0–0,75) | Минимум РАН к CAS задержка (тУЗО) | ||||||

| 30 | 0x1e | Наносекунды (1–255) | Минимальное время от активного до предварительной зарядки (tРАН) | |||||||

| 31 | 0x1f | 512 МБ | 256 МБ | 128 МБ | 16 ГиБ | 8 ГиБ | 4 ГиБ | 2 ГиБ | 1 ГиБ | Размер каждого ранга (битовая карта). |

| 32 | 0x20 | Десятые доли наносекунды (0,0–1,2) | Сотые доли наносекунд (0,00–0,09) | Время установки адреса / команды с часов | ||||||

| 33 | 0x21 | Десятые доли наносекунды (0,0–1,2) | Сотые доли наносекунд (0,00–0,09) | Время удержания адреса / команды после часов | ||||||

| 34 | 0x22 | Десятые доли наносекунды (0,0–0,9) | Сотые доли наносекунд (0,00–0,09) | Время настройки ввода данных из строба | ||||||

| 35 | 0x23 | Десятые доли наносекунды (0,0–0,9) | Сотые доли наносекунд (0,00–0,09) | Время удержания ввода данных после строба | ||||||

| 36 | 0x24 | Наносекунды (1–63) | 0,25 нс (0–0,75) | Минимальное время восстановления записи (tWR) | ||||||

| 37 | 0x25 | Наносекунды (1–63) | 0,25 нс (0–0,75) | Внутренняя задержка команды записи для чтения (tWTR) | ||||||

| 38 | 0x26 | Наносекунды (1–63) | 0,25 нс (0–0,75) | Внутреннее чтение для задержки команды предварительной зарядки (tRTP) | ||||||

| 39 | 0x27 | Зарезервированный | Зарезервировано для "анализа памяти характеристик зонда" | |||||||

| 40 | 0x28 | — | тRC дробные нс (0–5): 0, 0.25, 0.33, 0.5, 0.66, 0.75 | тRFC дробные нс (0–5): 0, 0.25, 0.33, 0.5, 0.66, 0.75 | тRFC + 256 нс | Расширение байтов 41 и 42. | ||||

| 41 | 0x29 | Наносекунды (1–255) | Минимальное время активности / активности / обновления (tRC) | |||||||

| 42 | 0x2a | Наносекунды (1–255) | Минимальное время обновления до активного / времени обновления (tRFC) | |||||||

| 43 | 0x2b | Наносекунды (0–15) | Десятые доли наносекунды (0,0–0,9) | Максимальное время цикла часов (tСК Максимум) | ||||||

| 44 | 0x2c | Сотые доли наносекунд (0,01–2,55) | Максимальный перекос, DQS на любой DQ. (тDQSQ Максимум) | |||||||

| 45 | 0x2d | Сотые доли наносекунд (0,01–2,55) | Коэффициент перекоса удержания считываемых данных (tQHS) | |||||||

| 46 | 0x2e | Микросекунды (1–255) | Время повторной блокировки PLL | |||||||

| 47–61 | 0x2f – 0x3d | Зарезервированный | Для будущей стандартизации. | |||||||

| 62 | 0x3e | Основная версия (0–9) | Незначительная доработка (0,0–0,9) | Уровень ревизии SPD, обычно 1.0 | ||||||

| 63 | 0x3f | Контрольная сумма | Сумма байтов 0–62, не отрицается | |||||||

| 64–71 | 0x40–47 | Производитель JEDEC ID | Сохраненный прямой порядок байтов, завершающий нулевой блок | |||||||

| 72 | 0x48 | Место изготовления модуля | Код производителя | |||||||

| 73–90 | 0x49–0x5a | Номер детали модуля | ASCII с заполнением пробелами (ограничено (, -,), A – Z, a – z, 0–9, пробел) | |||||||

| 91–92 | 0x5b – 0x5c | Код версии модуля | Код производителя | |||||||

| 93 | 0x5d | Годы с 2000 г. (0–255) | Дата изготовления (YYWW) | |||||||

| 94 | 0x5e | Недели (1–52) | ||||||||

| 95–98 | 0x5f – 0x62 | Серийный номер модуля | Код производителя | |||||||

| 99–127 | 0x63–0x7f | Данные производителя | Может быть улучшен профиль производительности | |||||||

DDR3 SDRAM

Стандарт DDR3 SDRAM значительно пересматривает и упрощает структуру содержимого SPD. Вместо ряда наносекундных полей в кодировке BCD некоторые единицы «временной развертки» задаются с высокой точностью, а различные параметры синхронизации кодируются как кратные этой базовой единице.[8] Кроме того, отказались от практики указания различных значений времени в зависимости от задержки CAS; теперь есть только один набор временных параметров.

Версия 1.1 позволяет выражать некоторые параметры как значение «средней временной развертки» плюс (со знаком, –128 +127) поправку «точной временной развертки». Обычно средняя временная развертка составляет 1/8 нс (125 пс), а точная временная развертка составляет 1, 2,5 или 5 пс. Для совместимости с более ранними версиями, в которых отсутствует коррекция, среднее значение временной базы обычно округляется в большую сторону, а значение коррекции отрицательное. Таким образом работают следующие ценности:

| Байт MTB | Байт FTB | Ценить |

|---|---|---|

| 12 | 34 | тСКмин, минимальный период времени |

| 16 | 35 | тAAmin, минимальное время задержки CAS |

| 18 | 36 | тУЗОmin, минимальная задержка от RAS # до CAS # |

| 20 | 37 | тRPmin, минимальная задержка предварительной зарядки строки |

| 21, 23 | 38 | тRCмин., минимальная задержка включения / выключения / предварительной зарядки |

| Байт | Кусочек | Примечания | ||||||||

|---|---|---|---|---|---|---|---|---|---|---|

| Декабрь | Шестигранник | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | |

| 0 | 0x00 | Исключить серийный номер из CRC | Всего байт SPD (undef / 256) | Используемые байты SPD (undef / 128/176/256) | ||||||

| 1 | 0x01 | Основная редакция СПД | Младшая доработка СПД | 1.0, 1.1, 1.2 или 1.3 | ||||||

| 2 | 0x02 | Базовый тип памяти (11 = DDR3 SDRAM) | Тип микросхем RAM | |||||||

| 3 | 0x03 | Зарезервированный | Тип модуля | Тип модуля; например, 2 = небуферизованный DIMM, 3 = SO-DIMM, 11 = LRDIMM | ||||||

| 4 | 0x04 | — | Биты адреса банка − 3 | бревно2(бит на чип) −28 | Ноль означает 8 банков, 256 Mibit. | |||||

| 5 | 0x05 | — | Биты адреса строки-12 | Биты адреса столбца-9 | ||||||

| 6 | 0x06 | Зарезервированный | 1,25 В | 1,35 В | Не 1,5 В | Поддерживаемые напряжения модулей. 1,5 В. По умолчанию. | ||||

| 7 | 0x07 | — | разряды − 1 | бревно2(Битов ввода / вывода / чип) -2 | Организация модуля | |||||

| 8 | 0x08 | — | Биты ECC (001 = 8) | бревно2(биты данных) −3 | 0x03 для 64-битных модулей DIMM без ECC. | |||||

| 9 | 0x09 | Дивиденд, пикосекунды (1–15) | Делитель, пикосекунды (1–15) | Fine Time Base, дивиденд / делитель | ||||||

| 10 | 0x0a | Дивиденд, наносекунды (1–255) | Средняя временная база, дивиденд / делитель; обычно 1/8 | |||||||

| 11 | 0x0b | Делитель, наносекунды (1–255) | ||||||||

| 12 | 0x0c | Минимальное время цикла tСКмин | Кратно МТБ | |||||||

| 13 | 0x0d | Зарезервированный | ||||||||

| 14 | 0x0e | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | Поддерживаемые задержки CAS (растровое изображение) |

| 15 | 0x0f | — | 18 | 17 | 16 | 15 | 14 | 13 | 12 | |

| 16 | 0x10 | Минимальное время задержки CAS, тAAмин | В кратных MTB; например, 80/8 нс. | |||||||

| 17 | 0x11 | Минимальное время восстановления записи, тWRмин | В кратных MTB; например, 120/8 нс. | |||||||

| 18 | 0x12 | Минимальное время задержки от RAS до CAS, тУЗОмин | В кратных MTB; например, 100/8 нс. | |||||||

| 19 | 0x13 | Минимальное время активной задержки от строки к строке, tRRDмин | В кратных MTB; например, 60/8 нс. | |||||||

| 20 | 0x14 | Минимальное время предварительной зарядки ряда, тRPмин | В кратных MTB; например, 100/8 нс. | |||||||

| 21 | 0x15 | тRCмин, биты 11: 8 | тРАНмин, биты 11: 8 | Старшие 4 бита байтов 23 и 22 | ||||||

| 22 | 0x16 | Минимальная активная по времени, тРАНmin, биты 7: 0 | В кратных MTB; например, 280/8 нс. | |||||||

| 23 | 0x17 | Минимум от активного до активного / обновления, tRCmin, биты 7: 0 | В кратных MTB; например, 396/8 нс. | |||||||

| 24 | 0x18 | Минимальная задержка восстановления восстановления, тRFCmin, биты 7: 0 | В кратных MTB; например, 1280/8 нс. | |||||||

| 25 | 0x19 | Минимальная задержка восстановления восстановления, тRFCмин, биты 15: 8 | ||||||||

| 26 | 0x1a | Минимальная внутренняя задержка записи на чтение, tWTRмин | В кратных MTB; например, 60/8 нс. | |||||||

| 27 | 0x1b | Минимальное внутреннее считывание до задержки предварительной зарядки, тRTPмин | В кратных MTB; например, 60/8 нс. | |||||||

| 28 | 0x1c | Зарезервированный | тFAWмин, биты 11: 8 | В кратных MTB; например, 240/8 нс. | ||||||

| 29 | 0x1d | Минимум четыре активации окна задержки tFAWmin, биты 7: 0 | ||||||||

| 30 | 0x1e | DLL-off | — | RZQ / 7 | RZQ / 6 | Дополнительные функции SDRAM поддерживают растровое изображение | ||||

| 31 | 0x1f | PASR | — | ODTS | ASR | ETR 1 × | ETR (95 ° C) | Параметры теплового режима SDRAM и обновления | ||

| 32 | 0x20 | Подарок | Точность (подлежит уточнению; в настоящее время 0 = не определено) | Есть термодатчик DIMM? | ||||||

| 33 | 0x21 | Nonstd. | Количество кубиков | — | Сигнальная нагрузка | Нестандартный тип устройства SDRAM (например, сложенный кристалл) | ||||

| 34 | 0x22 | тСКмин. поправка (новое в 1.1) | Знаковое кратное FTB, добавленное к байту 12 | |||||||

| 35 | 0x23 | тAAмин. поправка (новое в 1.1) | Знаковое кратное FTB, добавленное к байту 16 | |||||||

| 36 | 0x24 | тУЗОмин. поправка (новое в 1.1) | Знаковое кратное FTB, добавленное к байту 18 | |||||||

| 37 | 0x25 | тRPмин. поправка (новое в 1.1) | Знаковое кратное FTB, добавленное к байту 20 | |||||||

| 38 | 0x26 | тRCмин. поправка (новое в 1.1) | Знаковое кратное FTB, добавленное к байту 23 | |||||||

| 39–40 | 0x27–0x28 | Зарезервированный | Для будущей стандартизации. | |||||||

| 41 | 0x29 | Зависит от поставщика | тMAW | Максимальный счетчик активации (MAC) (непроверено / 700k / 600k /.../ 200k / зарезервировано / ∞) | За гребной молот смягчение | |||||

| 42–59 | 0x2a – 0x3b | Зарезервированный | Для будущей стандартизации. | |||||||

| 60 | 0x3c | — | Высота модуля, мм (1–31,> 45) | Номинальная высота модуля | ||||||

| 61 | 0x3d | Толщина спинки, мм (1–16) | Толщина фасада, мм (1–16) | Толщина модуля, значение = ceil (мм) - 1 | ||||||

| 62 | 0x3e | Дизайн | Редакция | Номер конструкции JEDEC | Использован эталонный дизайн JEDEC (11111 = нет) | |||||

| 63–116 | 0x3f – 0x74 | Специфичный для модуля раздел | Различия между зарегистрированными и небуферизованными | |||||||

| 117 | 0x75 | Идентификатор производителя модуля, лсбайт | Назначено JEP-106 | |||||||

| 118 | 0x76 | ID производителя модуля, мсбайт | ||||||||

| 119 | 0x77 | Место изготовления модуля | Код производителя | |||||||

| 120 | 0x78 | Десятки лет | Годы | Год изготовления (BCD) | ||||||

| 121 | 0x79 | Десятки недель | Недели | Производственная неделя (BCD) | ||||||

| 122–125 | 0x7a – 0x7d | Серийный номер модуля | Код производителя | |||||||

| 126–127 | 0x7e – 0x7f | СПД ЦРК-16 | Включает байты 0–116 или 0–125; см. байт 0 бит 7 | |||||||

| 128–145 | 0x80–0x91 | Номер детали модуля | Подмножество ASCII, заполненное пробелами | |||||||

| 146–147 | 0x92–0x93 | Код версии модуля | Определено поставщиком | |||||||

| 148–149 | 0x94–0x95 | ID производителя DRAM | В отличие от производителя модуля | |||||||

| 150–175 | 0x96–0xAF | Данные производителя | ||||||||

| 176–255 | 0xB0–0xFF | Доступно для использования клиентами | ||||||||

Емкость памяти модуля может быть вычислена из байтов 4, 7 и 8. Ширина модуля (байт 8), деленная на количество бит на чип (байт 7), дает количество чипов на ранг. Затем это можно умножить на емкость каждого кристалла (байт 4) и количество рангов микросхем в модуле (обычно 1 или 2, начиная с байта 7).

DDR4 SDRAM

Стандарт DDR4 SDRAM "Annex L" для SPD изменяет используемый модуль EEPROM. Вместо старых 256-байтовых EEPROM, совместимых с AT24C02, JEDEC теперь определяет новый нестандартный тип EE1004 с двумя страницами на уровне SMBus, каждая из которых имеет 256 байтов. В новой памяти по-прежнему используются старые адреса 0x50-0x57, но два дополнительных адреса 0x36 (SPA0) и 0x37 (SPA1) теперь используются для приема команд для выбора текущей активной страницы для шины, что является формой переключение банка.[11] Внутри каждая логическая страница делится на два физических блока по 128 байтов каждый, всего четыре блока по 512 байтов.[12] Другая семантика для "специальных" диапазонов адресов остается прежней, хотя защита от записи теперь адресуется блоками, и теперь требуется высокое напряжение на SA0 для изменения ее статуса.[13]

Приложение L определяет несколько различных макетов, которые могут быть включены в 512-байтовый (из которых определено максимум 320 байтов) шаблон, в зависимости от типа модуля памяти. Определения битов аналогичны DDR3.[12]

| Байт | Кусочек | Примечания | ||||||||

|---|---|---|---|---|---|---|---|---|---|---|

| Декабрь | Шестигранник | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | |

| 0 | 0x00 | Использовано байтов SPD | ||||||||

| 1 | 0x01 | Ревизия СПД n | Обычно 0x10, 0x11, 0x12 | |||||||

| 2 | 0x02 | Базовый тип памяти (12 = DDR4 SDRAM) | Тип микросхем RAM | |||||||

| 3 | 0x03 | Зарезервированный | Тип модуля | Тип модуля; например, 2 = небуферизованный DIMM, 3 = SO-DIMM, 11 = LRDIMM | ||||||

| 4 | 0x04 | Биты группы банков | Биты адреса банка − 2 | Общая емкость SDRAM на кристалл в МБ | Ноль означает отсутствие групп банков, 4 банка, 256 Mibit. | |||||

| 5 | 0x05 | Зарезервированный | Биты адреса строки-12 | Биты адреса столбца-9 | ||||||

| 6 | 0x06 | Тип первичного пакета SDRAM | Количество кубиков | Зарезервированный | Загрузка сигнала | |||||

| 7 | 0x07 | Зарезервированный | Максимальное окно активации (tMAW) | Максимальное количество активаций (MAC) | Дополнительные функции SDRAM | |||||

| 8 | 0x08 | Зарезервированный | Параметры теплового режима SDRAM и обновления | |||||||

| 9 | 0x09 | Почтовый ремонт пакетов (PPR) | Мягкий ППР | Зарезервированный | Другие дополнительные функции SDRAM | |||||

| 10 | 0x0a | Тип пакета SDRAM | Количество кубиков − 1 | Соотношение плотности DRAM | Загрузка сигнала | Тип вторичного SDRAM пакета | ||||

| 11 | 0x0b | Зарезервированный | Флаг Endurant | Действующий флаг | Номинальное напряжение модуля, ВДД | |||||

| 12 | 0x0c | Зарезервированный | Сочетание рангов | Количество пакетов на DIMM − 1 | Ширина устройства SDRAM | Организация модуля | ||||

| 13 | 0x0d | Зарезервированный | Увеличение ширины автобуса | Ширина основной шины | Разрядность шины памяти модуля в битах | |||||

| 14 | 0x0e | Термодатчик | Зарезервированный | Модуль термодатчика | ||||||

| 15 | 0x0f | Зарезервированный | Тип расширенного базового модуля | |||||||

| 16 | 0x10 | Зарезервированный | ||||||||

| 17 | 0x11 | Зарезервированный | Средняя временная развертка (MTB) | Точная шкала времени (FTB) | Измеряется в пс. | |||||

| 18 | 0x12 | Минимальное время цикла SDRAM, тCKAVGмин | В кратных MTB; например, 100/8 нс. | |||||||

| 19 | 0x13 | Максимальное время цикла SDRAM, тCKAVGМаксимум | В кратных MTB; например, 60/8 нс. | |||||||

| 20 | 0x14 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | Поддерживаемые задержки CAS битовая маска |

| 21 | 0x15 | 22 | 21 | 20 | 19 | 18 | 17 | 16 | 15 | Поддерживаемые задержки CAS битовая маска |

| 22 | 0x16 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | Поддерживаемые задержки CAS битовая маска |

| 23 | 0x17 | Низкий диапазон CL | Зарезервированный | 36 | 35 | 34 | 33 | 32 | 31 | Поддерживаемые задержки CAS битовая маска |

| 24 | 0x18 | Минимальное время задержки CAS, тAAмин | В кратных MTB; например, 1280/8 нс. | |||||||

| 25 | 0x19 | Минимальное время задержки от RAS до CAS, тRFCмин | В кратных MTB; например, 60/8 нс. | |||||||

| 26 | 0x1a | Минимальное время задержки предварительной зарядки ряда, тRPмин | В кратных MTB; например, 60/8 нс. | |||||||

| 27 | 0x1b | Верхние полубайты для tРАНмин и тRCмин | ||||||||

| 28 | 0x1c | Минимальное время задержки активного до предварительной зарядки, тРАНминимальный младший байт | Кратно МТБ | |||||||

| 29 | 0x1d | Минимальное время задержки от активного к активному / обновлению, tRCминимальный младший байт | Кратно МТБ | |||||||

| 30 | 0x1e | Минимальное время задержки восстановления восстановления, тRFC1минимальный младший байт | Кратно МТБ | |||||||

| 31 | 0x1f | Минимальное время задержки восстановления восстановления, тRFC1минимальный старший байт | Кратно МТБ | |||||||

| 32 | 0x20 | Минимальное время задержки восстановления восстановления, тRFC2минимальный младший байт | Кратно МТБ | |||||||

| 33 | 0x21 | Минимальное время задержки восстановления восстановления, тRFC2минимальный старший байт | Кратно МТБ | |||||||

| 34 | 0x22 | Минимальное время задержки восстановления восстановления, тRFC4минимальный младший байт | Кратно МТБ | |||||||

| 35 | 0x23 | Минимальное время задержки восстановления восстановления, тRFC4минимальный старший байт | Кратно МТБ | |||||||

| 36 | 0x24 | Зарезервированный | тFAWминимальный старший полубайт | |||||||

| 37 | 0x25 | Время задержки не менее четырех окон активации, тFAWминимальный младший байт | Кратно МТБ | |||||||

| 38 | 0x26 | Минимальное время активации для активации задержки, tRRD_Sмин, другая группа банков | Кратно МТБ | |||||||

| 39 | 0x27 | Минимальное время активации для активации задержки, tRRD_Sмин, та же группа банков | Кратно МТБ | |||||||

| 40 | 0x28 | Минимальное время задержки CAS в CAS, тCCD_Lмин, та же группа банков | Кратно МТБ | |||||||

| 41 | 0x29 | Верхний полубайт для tWRмин | ||||||||

| 42 | 0x2a | Минимальное время восстановления записи, тWRмин | Кратно МТБ | |||||||

| 43 | 0x2b | Верхние полубайты для tWTRмин | ||||||||

| 44 | 0x2c | Минимальное время записи на чтение, тWTR_Sмин, другая группа банков | Кратно МТБ | |||||||

| 45 | 0x2d | Минимальное время записи на чтение, тWTR_Lмин, та же группа банков | Кратно МТБ | |||||||

| 49–59 | 0x2e – 0x3b | Зарезервированный | Раздел базовой конфигурации | |||||||

| 60-77 | 0x3c-0x4d | Разъем для преобразования битов SDRAM | ||||||||

| 78–116 | 0x4e – 0x74 | Зарезервированный | Раздел базовой конфигурации | |||||||

| 117 | 0x75 | Точное смещение минимального времени задержки CAS в CAS, tCCD_Lмин, тот же банк | Множитель с дополнением до двух для блоков FTB | |||||||

| 118 | 0x76 | Точное смещение для минимальной активации для активации времени задержки, tRRD_Lмин, та же группа банков | Множитель с дополнением до двух для блоков FTB | |||||||

| 119 | 0x77 | Точное смещение для минимальной активации для активации времени задержки, tRRD_Sмин, другая группа банков | Множитель с дополнением до двух для блоков FTB | |||||||

| 120 | 0x78 | Точное смещение минимального времени задержки активного и активного / обновления, tRCмин | Множитель с дополнением до двух для блоков FTB | |||||||

| 121 | 0x79 | Точное смещение минимального времени задержки предварительной зарядки ряда, tRPмин | Множитель с дополнением до двух для блоков FTB | |||||||

| 122 | 0x7a | Точное смещение для минимального времени задержки RAS в CAS, tУЗОмин | Множитель с дополнением до двух для блоков FTB | |||||||

| 123 | 0x7b | Точное смещение для минимального времени задержки CAS, tAAмин | Множитель с дополнением до двух для блоков FTB | |||||||

| 124 | 0x7c | Точное смещение для максимального времени цикла SDRAM, тCKAVGМаксимум | Множитель с дополнением до двух для блоков FTB | |||||||

| 125 | 0x7d | Точное смещение минимального времени цикла SDRAM, тCKAVGмин | Множитель с дополнением до двух для блоков FTB | |||||||

| 126 | 0x7e | Циклический код избыточности (CRC) для раздела базовой конфигурации, младший байт | CRC16 алгоритм | |||||||

| 127 | 0x7f | Циклический код избыточности (CRC) для раздела базовой конфигурации, старший байт | CRC16 алгоритм | |||||||

| 128–191 | 0x80–0xbf | Специфичный для модуля раздел | Зависит от семейства модулей памяти (UDIMM, RDIMM, LRDIMM) | |||||||

| 192–255 | 0xc0–0xff | Параметры, специфичные для архитектуры гибридной памяти | ||||||||

| 256–319 | 0x100–0x13f | Блок расширенных функциональных параметров | ||||||||

| 320-321 | 0x140-0x141 | Производитель модуля | См. JEP-106. | |||||||

| 322 | 0x142 | Место изготовления модуля | Код места производства, определенный производителем | |||||||

| 323 | 0x143 | Год изготовления модуля | Представлено в двоично-десятичном формате (BCD) | |||||||

| 324 | 0x144 | Неделя изготовления модулей | Представлено в двоично-десятичном формате (BCD) | |||||||

| 325-328 | 0x145-0x148 | Серийный номер модуля | Определенный производителем формат уникального серийного номера для номеров деталей | |||||||

| 329-348 | 0x149-0x15c | Номер детали модуля | Номер детали ASCII, неиспользуемые цифры должны быть установлены на 0x20 | |||||||

| 349 | 0x15d | Код версии модуля | Код версии, определяемый производителем | |||||||

| 350-351 | 0x15e-0x15f | Идентификационный код производителя DRAM | См. JEP-106. | |||||||

| 352 | 0x160 | Степпинг DRAM | Определяемый производителем пошаговый режим или 0xFF, если не используется | |||||||

| 353–381 | 0x161–0x17d | Конкретные данные производителя | ||||||||

| 382–383 | 0x17e-0x17f | Зарезервированный | ||||||||

Расширения

Стандарт JEDEC определяет только некоторые байты SPD. По-настоящему важные данные помещаются в первые 64 байта,[6][7][15][16][17] а часть оставшейся суммы предназначена для идентификации производителя. Однако обычно предоставляется 256-байтовая EEPROM. Оставшееся пространство было использовано в ряде случаев.

Расширенные профили производительности (EPP)

Память обычно поставляется с консервативными рекомендациями по времени в SPD ROM, чтобы обеспечить базовую функциональность во всех системах. Энтузиасты часто тратят много времени на ручную настройку таймингов памяти для повышения скорости.

Enhanced Performance Profiles - это расширение SPD, разработанное Nvidia и Корсар, который включает дополнительную информацию для более эффективной работы DDR2 SDRAM, включая данные о напряжениях питания и синхронизации команд, не включенные в спецификацию JEDEC SPD. Информация EPP хранится в той же EEPROM, но в байтах 99–127, которые не используются стандартной DDR2 SPD.[18]

| Байтов | Размер | Полные профили | Сокращенные профили |

|---|---|---|---|

| 99–103 | 5 | Заголовок EPP | |

| 104–109 | 6 | Профиль FP1 | Профиль AP1 |

| 110–115 | 6 | Профиль AP2 | |

| 116–121 | 6 | Профиль FP2 | Профиль AP3 |

| 122–127 | 6 | Профиль AP4 | |

Параметры специально разработаны для установки контроллера памяти на nForce 5, nForce 6 и nForce 7 чипсеты. Nvidia поощряет поддержку EPP в BIOS для своих высокопроизводительных чипсетов материнских плат. Это предназначено для обеспечения "одним щелчком мыши" разгон"для повышения производительности с минимальными усилиями.

Nvidia называет память EPP, которая имеет квалификацию по производительности и стабильности, «память с поддержкой SLI».[19] Термин "SLI-ready-memory" вызвал некоторую путаницу, так как не имеет ничего общего с SLI видео. Можно использовать память EPP / SLI с одной видеокартой (даже с картой, отличной от Nvidia), и можно запустить настройку видео SLI с несколькими картами без памяти EPP / SLI.

Расширенная версия EPP 2.0 также поддерживает память DDR3.[20]

Экстремальный профиль памяти (XMP)

Похожий, Intel-разработанное расширение JEDEC SPD было разработано для DDR3 SDRAM Модули DIMM, позже используемые в DDR4 также. XMP использует байты 176–255, которые не выделены JEDEC, для кодирования таймингов памяти с более высокой производительностью.[21]

Позже AMD разработала AMP, технологию, эквивалентную XMP, для использования в линейке модулей памяти Radeon Memory, оптимизированных для использования на платформах AMD.[22][23] Кроме того, разработчики материнских плат реализовали свои собственные технологии, позволяющие материнским платам на базе AMD читать профили XMP: MSI предлагает A-XMP,[24] У ASUS есть DOCP (динамические профили разгона), а у Gigabyte есть EOCP (расширенные профили разгона).[25]

| DDR3 байтов | Размер | Использовать |

|---|---|---|

| 176–184 | 10 | Заголовок XMP |

| 185–219 | 33 | Профиль XMP 1 (настройки "энтузиастов") |

| 220–254 | 36 | Профиль XMP 2 («экстремальные» настройки) |

Заголовок содержит следующие данные. Наиболее важно то, что он содержит значение MTB для «средней временной развертки» как рациональное количество наносекунд (общие значения - 1/8, 1/12 и 1/16 нс). Многие другие более поздние значения синхронизации выражаются целым числом единиц MTB.

В заголовок также включено количество модулей DIMM на канал памяти, для поддержки которых предназначен профиль; включение большего количества модулей DIMM может не работать.

| DDR3 байт | Биты | Использовать |

|---|---|---|

| 176 | 7:0 | XMP магическое число байт 1 0x0C |

| 177 | 7:0 | Байт 2 магического числа XMP 0x4A |

| 178 | 0 | Профиль 1 включен (если 0, отключен) |

| 1 | Профиль 2 включен | |

| 3:2 | Профиль 1 DIMM на канал (1–4 в кодировке 0–3) | |

| 5:4 | Профиль 2 модуля DIMM на канал | |

| 7:6 | Зарезервированный | |

| 179 | 3:0 | Дополнительный номер версии XMP (x.0 или x.1) |

| 7:4 | Номер основной версии XMP (0.x или 1.x) | |

| 180 | 7:0 | Средний дивиденд по временной шкале для профиля 1 |

| 181 | 7:0 | Средний делитель временной развертки для профиля 1 (MTB = делитель / делитель нс) |

| 182 | 7:0 | Средний дивиденд по временной развертке для профиля 2 (например, 8) |

| 183 | 7:0 | Средний делитель временной развертки для профиля 2 (например, 1, что дает MTB = 1/8 нс) |

| 184 | 7:0 | Зарезервированный |

| DDR3 байт 1 | DDR3 байт 2 | Биты | Использовать |

|---|---|---|---|

| 185 | 220 | 0 | Модуль Vdd напряжения двадцатых (0,00 или 0,05) |

| 4:1 | Модуль Vdd напряжения десятых долей (0,0–0,9) | ||

| 6:5 | Модуль Vdd, единицы напряжения (0–2) | ||

| 7 | Зарезервированный | ||

| 186 | 221 | 7:0 | Минимальный тактовый период SDRAM tСКмин (единицы MTB) |

| 187 | 222 | 7:0 | Минимальное время задержки CAS tAAмин (единицы MTB) |

| 188 | 223 | 7:0 | Поддерживаются задержки CAS (битовая карта, 4–11, закодированные как биты 0–7) |

| 189 | 224 | 6:0 | Поддерживаемые задержки CAS (битовая карта, 12–18, закодированные как биты 0–6) |

| 7 | Зарезервированный | ||

| 190 | 225 | 7:0 | Минимальное время задержки записи CAS tCWLмин (единицы MTB) |

| 191 | 226 | 7:0 | Минимальное время задержки предварительной зарядки ряда tRPмин (единицы MTB) |

| 192 | 227 | 7:0 | Минимальное время задержки от RAS до CAS tУЗОмин (единицы MTB) |

| 193 | 228 | 7:0 | Минимальное время восстановления записи tWRмин (единицы MTB) |

| 194 | 229 | 3:0 | тРАНмин верхний грызть (биты 11: 8) |

| 7:4 | тRCмин. верхний полубайт (биты 11: 8) | ||

| 195 | 230 | 7:0 | Минимальное время задержки активного до предварительной зарядки tРАНмин. биты 7: 0 (единицы MTB) |

| 196 | 231 | 7:0 | Минимальное время задержки от активного к активному / обновления tRCмин. биты 7: 0 (единицы MTB) |

| 197 | 232 | 7:0 | Максимальный средний интервал обновления tREFI lsbyte (единицы MTB) |

| 198 | 233 | 7:0 | Максимальный средний интервал обновления tREFI мсбайт (единицы MTB) |

| 199 | 234 | 7:0 | Минимальное время задержки восстановления tRFCmin lsbyte (единицы MTB) |

| 200 | 235 | 7:0 | Минимальное время задержки восстановления tRFCмин. мсбайт (единицы MTB) |

| 201 | 236 | 7:0 | Минимальное внутреннее считывание для времени задержки команды предварительной зарядки tRTPмин (единицы MTB) |

| 202 | 237 | 7:0 | Минимальное время задержки от активной строки до активной строки tRRDмин (единицы MTB) |

| 203 | 238 | 3:0 | тFAWмин. верхний полубайт (биты 11: 8) |

| 7:4 | Зарезервированный | ||

| 204 | 239 | 7:0 | Минимум четыре времени задержки активации окна tFAWмин. биты 7: 0 (единицы MTB) |

| 205 | 240 | 7:0 | Минимальное внутреннее время задержки команды записи для чтения tWTRмин (единицы MTB) |

| 206 | 241 | 2:0 | Настройка времени выполнения команды записи для чтения (0–7 тактов) |

| 3 | Запись, чтобы прочитать знак регулировки поворота команды (0 = втягивание, 1 = выдвижение) | ||

| 6:4 | Регулировка времени выполнения команды чтения для записи (0–7 тактов) | ||

| 7 | Чтение и запись знака регулировки поворота команды (0 = втягивание, 1 = выдвижение) | ||

| 207 | 242 | 2:0 | Последовательная регулировка времени выполнения команд (0–7 тактов) |

| 3 | Знак регулировки поворота спина к спине (0 = втягивание, 1 = выдвижение) | ||

| 7:4 | Зарезервированный | ||

| 208 | 243 | 7:0 | Системный режим скорости CMD. 0 = JTAG по умолчанию, иначе в особых единицах MTB × tСК/ нс. Например. если MTB составляет 1/8 нс, то это единицы, равные 1/8 тактового цикла. |

| 209 | 244 | 7:0 | Производительность автоматического самообновления SDRAM. Стандартная версия 1.1 говорит, что документация TBD. |

| 210–218 | 245–253 | 7:0 | Зарезервированный |

| 219 | 254 | 7:0 | Зарезервированный, индивидуальный код поставщика. |

Все данные выше относятся к DDR3 (XMP 1.1); Спецификации DDR4 пока недоступны.

Память конкретного производителя

Распространенное неправильное использование - запись информации в определенные области памяти для привязки модулей памяти конкретного производителя к конкретной системе. Технологические решения Fujitsu , как известно, делает это. Добавление другого модуля памяти в систему обычно приводит к отказу или другим ответным мерам (например, нажатие F1 при каждой загрузке).

02 0E 00 01-00 00 00 EF-02 03 19 4D-BC 47 C3 46 ........... MGF53 43 00 04-EF 4F 8D 1F-00 01 70 00-01 03 C1 CF СК ... О .... п .....

Это результат модуля памяти на 512 МБ от Micron Technologies, выпускаемого для Fujitsu-Siemens Computers, обратите внимание на строку «FSC». Системная BIOS отклоняет модули памяти, которые не имеют этой информации, начиная со смещения 128h.

Некоторые ноутбуки Packard Bell AMD также используют этот метод, в этом случае симптомы могут отличаться, но это может привести к миганию курсора, а не к звуковому сигналу. Кстати, это тоже может быть признаком повреждения BIOS.[27] Хотя обновление 2 ГБ до 4 ГБ также может привести к проблемам.

Чтение и запись информации SPD

Производители модулей памяти записывают информацию о SPD в EEPROM на модуле. Материнская плата BIOS прочтите информацию SPD, чтобы настроить контроллер памяти. Существует несколько программ, которые могут считывать и изменять информацию SPD на большинстве, но не на всех наборах микросхем материнских плат.

- dmidecode программа, которая может декодировать информацию о памяти (и других вещах) и работает на Linux, FreeBSD, NetBSD, OpenBSD, BeOS, Cygwin и Солярис. dmidecode не имеет прямого доступа к информации SPD; он сообщает данные BIOS о памяти.[28] Эта информация может быть ограниченной или неверной.

- На Linux системы, пространство пользователя программа decode-dimms, поставляемая с i2c-tools, декодирует и печатает информацию в любой памяти с информацией SPD в компьютере.[29] Это требует SMBus поддержка контроллера в ядре, драйвер ядра EEPROM, а также подключение SPD EEPROM к SMBus. В старых дистрибутивах Linux decode-dimms.pl был доступен как часть lm датчики.

- OpenBSD включает драйвер (spdmem (4)) начиная с версии 4.3 для предоставления информации о модулях памяти. Драйвер был перенесен из NetBSD, где он доступен с версии 5.0.

- Coreboot читает и использует информацию SPD для инициализации всех контроллеры памяти в компьютере с таймингом, размером и другими свойствами.

- Windows системы используют такие программы, как HWiNFO32,[30] CPU-Z и Speccy, который может считывать и отображать информацию о модуле DRAM из SPD.

Независимое от чипсета чтение и запись информации SPD осуществляется путем прямого доступа к EEPROM памяти с помощью аппаратного и программного обеспечения программатора eeprom.

Не так распространено использование старых ноутбуков в качестве универсальных считывателей SMBus, поскольку внутренняя EEPROM на модуле может быть отключена после того, как BIOS прочитает ее, поэтому шина по существу доступна для использования. Используемый метод заключается в понижении уровня линий A0, A1, чтобы внутренняя память отключилась, позволяя внешнему устройству получить доступ к SMBus. Как только это будет сделано, пользовательская сборка Linux или приложение DOS сможет получить доступ к внешнему устройству. Обычно используется восстановление данных с микросхем памяти ЖК-панели для модернизации стандартной панели в проприетарном ноутбуке. На некоторых микросхемах также рекомендуется разделить линии защиты от записи, чтобы встроенные микросхемы не стирались во время перепрограммирования. перезаписывает чип на веб-камерах, которые часто входят в комплект поставки многих ноутбуков, поскольку скорость шины значительно выше и может даже быть изменена так, чтобы 25x совместимые чипы могли быть считаны для последующего клонирования uEFI в случае отказа чипа.

К сожалению, это работает только с DDR3 и ниже, поскольку DDR4 использует другую безопасность и обычно может быть только прочитан. Можно использовать такой инструмент, как SPDTool или аналогичный, и заменить чип на тот, у которого свободна линия WP, чтобы его можно было изменить на месте. На некоторых наборах микросхем появляется сообщение «Несовместимый драйвер SMBus?» можно увидеть, поэтому чтение также запрещено.

Управление светодиодом RGB

Новые модули DIMM[31] иногда поддерживают светодиоды RGB, которые управляются проприетарными командами SMBus. Это позволяет управлять светодиодами без дополнительных разъемов и кабелей.

На старом оборудовании

Некоторое старое оборудование требует использования SIMM с параллельно обнаружение присутствия (чаще называется просто обнаружение присутствия или PD). Некоторое оборудование использует нестандартное кодирование PD, IBM компьютеры и Hewlett Packard LaserJet и, в частности, другие принтеры.

Смотрите также

Рекомендации

- ^ Томас П. Кениг; Натан Джон (3 февраля 1997 г.), "Обнаружение последовательного присутствия готово к всеобщему вниманию", Электронные новости, 43 (2153)

- ^ Стандарт JEDEC 21-C, раздел 4.1.4 «Определение EEPROM для последовательного обнаружения присутствия (SPD) TSE2002av с датчиком температуры (TS) для приложений модуля памяти»

- ^ «TN-04-42: Защита от записи с обнаружением последовательного присутствия модуля памяти» (PDF). Микрон.

- ^ Примечание по применению INN-8668-APN3: Стандарты данных SDRAM SPD, memorytesters.com

- ^ Спецификация PC SDRAM Serial Presence Detect (SPD) (PDF), 1.2A, декабрь 1997 г., стр. 28

- ^ а б Стандарт JEDEC 21-C, раздел 4.1.2.4 «SPD для DDR SDRAM»

- ^ а б Стандарт JEDEC 21-C, раздел 4.1.2.10 «Специальные SPD для DDR2 SDRAM»

- ^ «Общие сведения о таблице обнаружения последовательного присутствия DDR3 (SPD)».

- ^ JESD21-C, приложение K: обнаружение последовательного присутствия для модулей DDR3 SDRAM, Выпуск 4, Версия 1.1 SPD

- ^ JESD21-C, приложение K: обнаружение последовательного присутствия для модулей DDR3 SDRAM, Выпуск 6, Версия 1.3 SPD

- ^ Дельвар, Жан. «[PATCH] eeprom: новый драйвер ee1004 для памяти DDR4». LKML. Получено 7 ноября 2019.

- ^ а б JEDEC. «Приложение L: обнаружение последовательного присутствия (SPD) для модулей DDR4 SDRAM» (PDF).

- ^ JEDEC. «Спецификация устройств EE1004 и TSE2004 (проект)» (PDF). Получено 7 ноября 2019.

- ^ JESD21-C, приложение L: обнаружение последовательного присутствия для модулей DDR4 SDRAM, Выпуск 5

- ^ Стандарт JEDEC 21-C, раздел 4.1.2.11 «Обнаружение последовательного присутствия (SPD) для модулей DDR3 SDRAM»

- ^ Стандарт JEDEC 21-C, раздел 4.1.2 «СТАНДАРТ ПОСЛЕДОВАТЕЛЬНОГО ПРИСУТСТВИЯ, Общий стандарт»

- ^ Стандарт JEDEC 21-C, раздел 4.1.2.5 «Конкретные PD для синхронной DRAM (SDRAM)»

- ^ Спецификация проектирования профилей повышенной производительности DDR2 UDIMM (PDF), Nvidia, 12 мая 2006 г., получено 5 мая 2009

- ^ http://www.nvidia.com/docs/CP/45121/sli_memory.pdf

- ^ Расширенные профили производительности 2.0 (стр. 2–3)

- ^ «Поддержка Intel». Intel.

- ^ Advanced Micro Devices, Inc (2012 г.). «Технология профиля памяти - увеличьте объем оперативной памяти». Получено 8 января 2018.

- ^ Райан Мартин (23 июля 2012 г.). «AMD представляет свой XMP-эквивалент AMP - eTeknix». Получено 8 января 2018.

- ^ Micro-Star Int'l Co., Ltd (21 марта 2017 г.). «MSI - первый в мире бренд, который поддерживает A-XMP на Ryzen для лучшей производительности DDR4, запускает новые модели». Получено 8 января 2018.

- ^ Tradesman1 (26 августа 2016 г.). "Что означает XMP, DOCP, EOCP - Решено - Память". Получено 8 января 2018.

- ^ а б c Спецификация Intel Extreme Memory Profile (XMP), версия 1.1 (PDF), Октябрь 2007 г., архивировано из оригинал (PDF) 6 марта 2012 г., получено 25 мая 2010

- ^ "Обновление RAM Packard Bell LJ65". Форум Tom's Hardware.

- ^ "dmidecode: для чего он нужен?". Linux.com | Источник информации о Linux. 29 ноября 2004 г.

- ^ "декодировать-диммы (1)". Справочная страница Ubuntu. Получено 9 ноября 2019.

- ^ «HWiNFO - Профессиональная системная информация и диагностика». HWiNFO.

- ^ "Память VENGEANCE RGB PRO серии DDR4 | Память для настольных ПК | CORSAIR". www.corsair.com. Получено 26 ноября 2020.

внешняя ссылка

- Стандарт последовательного обнаружения присутствия, общий стандарт

- SPD Rev1.0 для DDR SDRAM

- SPD Rev1.2 для DDR2 SDRAM

- SPD Rev1.3 для DDR2 SDRAM

- СПЕЦИАЛЬНОСТЬ DDR2-1066 SDRAM

- Пакет Linux i2c-инструменты

- Инструкции по использованию lm-сенсоров или i2c-tools для чтения данных

- Производительность памяти: от 16 ГБ DDR3-1333 до DDR3-2400 на Ivy Bridge IGP с G.Skill - объяснение различных значений времени